# International Journal of Engineering

TEACHNICAL NOTE

Journal Homepage: www.ije.ir

# A Novel Design of Reversible Multiplier Circuit

#### P. Moallem\*a, M. Ehsanpourb

<sup>a</sup> Department of Electrical Engineering, University of Isfahan, Isfahan, Iran.

<sup>b</sup> Department of Computer, Falavarjan Branch, Islamic Azad University, Falavarjan, Isfahan, Iran

#### PAPER INFO

## ABSTRACT

Paper history: Received 22 June 2012 Received in revised form 5 January 2013 Accepted 24 January 2013

Keywords: Reversible Circuit Reversible Multiplier Reversible Gate Quantum Parameters Adders and multipliers are two main parts of arithmetic units of computer hardware and play important role in reversible computations. This paper introduces a novel reversible  $4\times4$  multiplier circuit that is based on an advanced "Partial Product Generation Circuits" (PPGC) with Peres gates only without duplicating gates. Again, an optimized Peres full adder reversible gate is used in "Reversible Parallel Adder" (RPA) part with accompaniment with the carry save adder technique. Comparison of the proposed design with previous ones shows that the proposed reversible multiplier improves the quantum parameters. The proposed design shows lower quantum cost and depth with the help of a novel design in PPGC. The circuit cost of the proposed design is a little higher than the best compared design, but the proposed design shows the lowest total cost which is defined as sum of quantum cost and circuit cost. Moreover, the number of gates, garbage input and output has no change regarding to the best compared design. The proposed multiplier can be generalized as an n×n bit multiplication.

doi: 10.5829/idosi.ije.2013.26.06c.03

| NOMEN | OMENCLATURE              |      |                                     |  |  |

|-------|--------------------------|------|-------------------------------------|--|--|

| ALU   | Arithmetic Logic Unit    | MKG  | Majid Keivan Gate                   |  |  |

| CC    | Circuit Cost             | NG   | New Gate                            |  |  |

| CPA   | Carry Propagating Adder  | NoG  | Number of Gates                     |  |  |

| CSA   | Carry Save Adder         | Ov   | Output Vector                       |  |  |

| D     | Depth                    | PA   | Parallel Adder                      |  |  |

| DSP   | Digital Signal Processor | PFAG | Peres Full Adder Gate               |  |  |

| FA    | Full Adder               | PG   | Peres Gate                          |  |  |

| FG    | Feynman Gate             | PPGC | Partial Product Generation Circuits |  |  |

| FRG   | Fredkin Gate             | QC   | Quantum Cost                        |  |  |

| Gin   | Garbage Input            | RPA  | Reversible Parallel Adder           |  |  |

| Gout  | Garbage Outputs          | ТС   | Total Cost                          |  |  |

| HA    | Half Adder               | TG   | Toffoli Gate                        |  |  |

| HNG   | Haghparast Navi Gate     | TSG  | Thapliyal Srinivas Gate             |  |  |

| $I_V$ | Input Vector             | VLSI | Very Large Scale Integrated         |  |  |

## **1. INTRODUCTION**

Power dissipation is one of the important parameters in the digital circuit design. A part of this energy loss is due to non-ideality of switches and other technological factors. Another part according to Landauer's principle [1] is due to irreversible logic computations that results in the energy dissipation as data loss. Irreversible circuits dissipate *KTln2* joules of energy for every bit of information that is lost regardless of their implementation technologies, where  $K=1.38\times10^{-23}$   $m^2kg^2k^1$  (Joules Kelvin<sup>-1</sup>) is the Boltzmann's constant,

<sup>\*</sup>Corresponding Author Email: p\_moallem@eng.ui.ac.ir (P. Moallem)

and T is the absolute temperature at which the computation is performed.

Due to irreversible gates, the power loss is negligible for current logic technologies using adiabatic design. However, it is well known that Moore's law, which states that processing power will double every 18 months, will stop functioning in the years 2010-2020. This particular problem of VLSI designing was realized by Feynman and Bennet in 1970s [2].

In 1973, Bennet [3] showed that energy dissipation problem of VLSI circuits can be circumvented by using reversible logics that will not loose energy during internal calculations (However, energy may be lost for input and output operations). Furthermore, the reversible logics will finally need hardware for the implementation. Quantum gates are inherently reversible [4], so that quantum computation can be considered as a basis for reversible logic implementations.

introduction reversible logics and An on corresponding parameters are presented in the Appendix. Reversible circuits for different purposes e.g. HA (Half Adder), FA (Full Adder) [5-7] and multiplier [8-12] have been proposed recently. Among these reversible circuits, multiplier circuits are of special importance because they are widely used in every modern ALU (Arithmetic Logic Unit) of computer system and DSP (Digital Signal Processor). Consequently, optimized multipliers are on demand while designing an arithmetic unit [13].

Several reversible logic gates have been proposed in the literature, including  $2\times 2$  Feynman gate (FG) [14],  $3\times 3$  Toffoli gate (TG) [15],  $3\times 3$  Fredkin gate (FRG) [16],  $3\times 3$  Peres gate (PG) [17],  $3\times 3$  New gate (NG) [18],  $4\times 4$  TSG gate [5],  $4\times 4$  MKG gate[6],  $4\times 4$  HNG gate[7] and  $4\times 4$  PFAG gate [11]. Significant aspect of these universal  $4\times 4$  reversible gates is that they can work singly as a reversible FA. Table 1 presents these reversible gates including their quantum implementation, cost and depth.

Among these reversible logic gates, several 4×4 reversible gates (e.g. TSG [5], MKG [6], HNG [7] and PFAG [11]) have been used in reversible multiplier designing to construct the FA.

In this paper, a novel reversible  $4\times4$  multiplier is designed which improves the quantum parameters and can be generalized to construct fast reversible n×n bit multipliers. The proposed reversible PPGC (Partial Product Generation Circuits) has minimum quantum cost among all the reversible PPGC designs in reversible multiplier circuits literature.

The related works in reversible multiplier circuit's designs is presented in Section 2. Our proposed reversible multiplier circuit design is described in Section 3. The comparisons and discussion about the results of the proposed design and the previous ones are

described in Sections 4 and 5, and finally Section 6 concludes the paper.

**TABLE 1.** Reversible gates, their quantum implementation, quantum cost (QC) and depth (D).

| Reversible gates                                                                                                                                                                                                                                        | Quantum implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | QC | D |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|

| $ \begin{array}{c} A \\ B \end{array} \begin{bmatrix} FG \\ Q = A \oplus B \end{array} $                                                                                                                                                                | $A - \Phi P = A$ $B - \Phi Q = A \oplus B$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1  | 1 |

| $ \begin{array}{c} A \\ B \\ C \end{array}  \begin{array}{c} P = A \\ Q = B \\ R = AB \oplus C \end{array} $                                                                                                                                            | $A \xrightarrow{P=A} P=A$ $B \xrightarrow{Q=B} Q=B$ $C \xrightarrow{R} R= A.B \oplus C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5  | 2 |

| A<br>B<br>C<br>FRG<br>P = A<br>$Q = A'B \oplus AC$<br>$R = A'C \oplus AB$                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5  | 3 |

| $ \begin{array}{c} A \\ B \\ C \end{array} \begin{array}{c} PG \\ R = A \oplus B \\ R = A B \oplus C \end{array} $                                                                                                                                      | $\begin{array}{c} A \\ B \\ C \\ C \\ \end{array} \begin{array}{c} P \\ P \\ Q \\ R \\ \end{array} \begin{array}{c} A \\ B \\ \end{array} \begin{array}{c} P \\ B \\ \end{array} \begin{array}{c} A \\ P \\ B \\ \end{array} \begin{array}{c} P \\ B \\ \end{array} \begin{array}{c} Q \\ B \\ \end{array} \begin{array}{c} P \\ B \\ \end{array} \begin{array}{c} Q \\ B \\ \end{array} \begin{array}{c} Q \\ \end{array} \begin{array}{c} P \\ B \\ \end{array} \begin{array}{c} Q \\ \end{array} \begin{array}{c} R \\ \end{array} \begin{array}{c} R \\ \end{array} \begin{array}{c} Q \\ \end{array} \begin{array}{c} R \\ \end{array} \end{array} \begin{array}{c} R \\ \end{array} \begin{array}{c} R \\ \end{array} \begin{array}{c} R \\ \end{array} \end{array} \begin{array}{c} R \\ \end{array} \begin{array}{c} R \\ R \end{array} \begin{array}{c} R \\ \end{array} \end{array} \begin{array}{c} R \\ \end{array} \end{array} \begin{array}{c} R \\ R \\ \end{array} \end{array} \begin{array}{c} R \\ \end{array} \end{array} \begin{array}{c} R \\ R \\ R \end{array} \end{array} $ \end{array} \left( R \\ R \\ R \\ R \end{array} \left( R \\ R \\ R \\ R \end{array} \right \left( R \\ R \\ R \\ R \end{array} \right) \left( R \\ R \\ R \\ R \\ R \\ R \\ R \end{array} \right) \left( R \\ R | 4  | 2 |

| $ \begin{array}{c} A \\ B \\ C \end{array} \begin{array}{c} P = A \\ Q = A B \oplus C \\ R = A' C' \oplus B' \end{array} $                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7  | 3 |

| $ \begin{array}{c} A \\ B \\ C \\ D \end{array} \\ \left[ \begin{array}{c} TSG \\ R \end{array} \right] = \begin{array}{c} P = A \\ Q = A' C' \oplus B' \\ R = (A' C' \oplus B') \oplus D \\ R = (A' C' \oplus B') D \oplus (AB \oplus C) \end{array} $ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14 | 5 |

| $ \begin{array}{c} A \\ B \\ C \\ D \end{array} \\ \end{tabular} \begin{array}{c} P = A \\ Q = C \\ R = (A \ D' \oplus B') \oplus C \\ S = (A \ D' \oplus B') C \oplus (A B \oplus D) \end{array} $                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 | 5 |

| $ \begin{array}{c} A \\ B \\ C \\ D \end{array} \\ \begin{array}{c} P = A \\ Q = B \\ R = A \oplus B \oplus C \\ S = (A \oplus B) \cdot C \oplus A B \oplus D \end{array} $                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  | 4 |

| A<br>B<br>C<br>PFAG<br>D<br>P = A<br>$Q = A \oplus B$<br>$R = A \oplus B \oplus C$<br>$S = (A \oplus B).C \oplus AB \oplus D$                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  | 4 |

#### 2. RELATED WORKS

The operation of a  $4\times4$  parallel multiplier is depicted in Figure 1. It can be applied to any other  $n\times n$  reversible multiplier. The existing parallel multiplier circuits have two important components: The PPGC and multiplier is reversible if its components; PPGC and PA both are reversible.

The operation of the reversible PPGC consists of 16 partial product bits of form  $x_i . y_i$ , where i,j=0, 1, 2, 3.

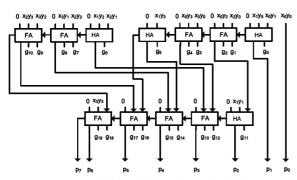

The parallel adder as shown in Figure 2 uses the FAs and HAs to produce final results. Some reversible gates including TSG, MKG, HNG and PFAG can be used as reversible FA.

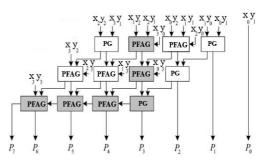

Different designs of parallel reversible multipliers circuits are described in the literature. In the first design that was introduced in 2005, FRGs were used for designing of PPGC part of this circuit and TGs, NGs were used for RPA (Reversible Parallel Adder) design [8]. Another reversible multiplier circuit that was introduced in 2006 used parallel FRGs as PPGC and TSGs as FAs and HAs in RPA section [9]. Another reversible multiplier circuit which was introduced in 2008 is PPGC design that is base on use of PGs instead of FRGs (see Figure 3) [10]. This circuit uses PGs since it has less logical calculation and less quantum cost in compare to FRGs. The operation of RPA of such circuit can be planned with MKGs as FAs and HAs [10]. Other reversible multiplier circuit that was introduced in 2008 used PG as HA and HNG as FA in RPA section of the circuit which is resulted in more desired circuits than the previous one [7]. Another circuit suggested in 2009 applied PFAG instead of HNG. This yielded in similar results with HNG gate due to its similar quantum implementation [11].

It is worth to be noted that in reversible logics, fanout of any gate output is not allowed and every output can be used only once. The  $2\times 2$  FG with one "0" input can be used as copying circuits to duplicate the fan-out.

|                       |                |          | ×                             | Х3<br>У3                      | Х <u>2</u><br>У2              | х <u>1</u><br>У1              | Х <sub>0</sub><br>Уо          |

|-----------------------|----------------|----------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

|                       |                |          |                               | x <sub>3</sub> y <sub>0</sub> | x <sub>2</sub> y <sub>0</sub> | x <sub>1</sub> y <sub>0</sub> | x <sub>0</sub> y <sub>0</sub> |

|                       |                |          | $x_3y_1$                      | x <sub>2</sub> y <sub>1</sub> | $x_1y_1$                      | x <sub>0</sub> y <sub>1</sub> |                               |

|                       |                | X3Y2     | x <sub>2</sub> y <sub>2</sub> | $x_1y_2$                      | x <sub>0</sub> y <sub>2</sub> |                               |                               |

|                       | X3Y3           | $x_2y_3$ | $x_1y_3$                      | x <sub>0</sub> y <sub>3</sub> |                               |                               |                               |

| <b>P</b> <sub>7</sub> | P <sub>6</sub> | P5       | P4                            | P3                            | <b>P</b> <sub>2</sub>         | P <sub>1</sub>                | P <sub>0</sub>                |

Figure 1. Operation of a 4×4 multiplication

**Figure 2.** 4×4 reversible multiplier circuit in which output of PPGC are input of parallel adder

Figure 3. Reversible PPGC using 16 Peres gates

rigure 4. Reversible 11 de with 1 ds and 1 ds

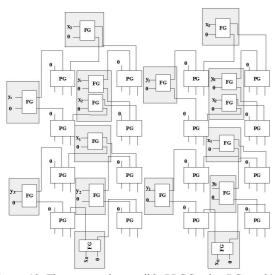

The duplicating gates in the previous designs [7-11] are the most disadvantages which degrade the quantum parameters. In order to remove these duplicating gates, the other suggested circuits in 2009 offered different design in PPGC part, as shown in Figure 4. Use of TGs and PGs for generating of partial products, had better results in numbers of garbage outputs, constant inputs and reversible gates compared to the previous designs [12]. There are two designs in RPA part of this circuit. The first design uses an optimized HNG FA as reversible FA and the second approach uses PFAG (Peres Full Adder Gate). In addition, they need four reversible HAs that use PG as reversible HA.

### **3. THE PROPOSED MULTIPLIER CIRCUIT**

As mentioned before, a reversible  $4 \times 4$  multiplier circuit has two important parts: PPGC and RPA. The purpose of this paper is the design of reversible multiplier circuits with the aim of improving the quantum parameters without losing its efficiency.

**3. 1. PPGC** Implementation of the PPGC of the proposed reversible multiplier circuit is based on the PPGC described elsewhere [12]. Since the Peres gate (PG) quantum cost is less than Toffoli gate (TG), therefore we replace TGs with PGs. One sample of replacing TG with PG is shown by the dashed rectangle in Figure 4. Applying PGs instead of TGs (see Figure 5) results in the proposed PPGC which uses only PGs as shown in Figure 6.

This circuit has an intrinsic advantage over others. As it is made up of same gates, it is easy to implement. Again, PGs have less QC than the TGs (see Table 1). Thus, we have found that the proposed PPGC block with lowest QC can be achieved through PGs.

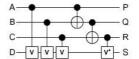

3. 2. RPA Circuit The basic cell in a reversible multiplier is a reversible FA which accepts three bits and one constant input. We use Peres FA gate (PFAG) [11] as a reversible FA that is shown in Figure 7. The PFAG can be implemented by two complex 4×4 reversible Peres gate as shown in Figure 8. Because of its complex functionality, it seems that the PFAG has a large QC of 8. But, implementation of the PFAG in 2009 [19] proved that it has QC of 6 and circuit depth of 4. As a result, its quantum cost is lower than other reversible FAs available in the literature and has the minimum QC reported for FA (see Figure 9). In order to decrease the circuit depth, the CSA (Carry Save Adder) technique can be used in implementing of the RPAs [20] of the proposed multiplier. As shown in Figure 1, in the reversible 4×4 multiplier, four operands must be added to produce the final product. We use the CSA tree to reduce the four operands to two. Thereafter, the CPA (Carry Propagating Adder) adds these two operands and produces the final 8-bit product (see Figure 10). However, this implementation leads the designer to take less depth than prior designs. Finally, we apply the reversible PFAG as a FA and PG as a HA to implement this part as shown in Figure 11. In this figure, the shaded blocks indicate the critical path of this circuit.

**Figure 5.** Use of the Peres gate instead of the Toffoli gate. (A) TG, (B) PG

Figure 6. The proposed reversible PPGC with only PGs

Figure 7. Reversible PFAG as a reversible FA

| Α – |    | — G₁ | с – |    | - G2               |

|-----|----|------|-----|----|--------------------|

| в – | PG |      |     | PG | – Sum              |

| 0 — |    |      |     |    | – C <sub>out</sub> |

Figure 8. Implementation of PFAG using Peres gates

Figure 9. Quantum implementation of PFAG

|     | • | : | • | •<br>•<br>• | •<br>•<br>• | • | • |

|-----|---|---|---|-------------|-------------|---|---|

|     | • | • | • | •           | •           | • | • |

| CPA | • | • | • | •           | •           | • | ٠ |

|     |   |   |   | •           | •           |   |   |

Figure 10. Four-operand Addition (Dot notation) [20]

Figure 11. The proposed RPA circuit using PFAG

# 4. QUANTUM PARAMETERS OF DIFFERENT DESIGNS

Some quantum parameters of the proposed multiplier as well as some other ones [8-12] are calculated in this section. As mentioned before, in reversible logics, fanout of any gate output is not allowed and every output can be used only once. Therefore, FGs should be used for duplicating each bit of the operands in reversible PPGC [7-11]. It is worth to be noted that PPGC proposed in [12] used 12 FGs for duplicating gates but that design approach did not pay enough consideration to numbers of FGs. Actually, all conclusions of that paper were wrong because of those errors. Another design was suggested in 2010 [21] rebuild PPGC with 16FGs instead of 12 FGs (see Figure 12).

Here we use correct approach [21] and believe that for duplicating fan-out, 16 FGs is necessary which increase the quantum parameters. Since the quantum cost and depth of  $2\times 2$  FG is one, the number of gates, circuit cost and number of constant inputs, quantum cost and depth in [7-12] should be added with 16 FG, because of its PPGC part.

**4. 1. Number of Gates** One of the major constraints in designing a reversible logic circuit is the number of reversible gates. For an arbitrary circuit *C* with *K* gates  $g_1,g_2,...,g_k$ , the number of gates metric is defined as NoG=k [22]. The NoG of the compared designs are shown in Table 2.

**4. 2. Garbage Output** Garbage output (Gout) refers to the output of the reversible gate that is not used as a primary output or as input to other gates. The garbage outputs of the compared designs are shown in Table 3.

**Figure 12.** The proposed reversible PPGC using PGs and FGs [21]

**4.3. Quantum Cost and Total Cost** Quantum cost (QC) is one of the other main factors in designing a reversible logic circuit. Again, in order to consider the effects of garbage output and number of gate as the accompaniment to quantum cost, the total cost (TC) of a circuit is defined as sum of number of gate, garbage outputs and quantum cost [19]. The quantum costs and total costs of the compared designs are shown in Table 4.

**TABLE 2.** Comparison of number of gates (NoG) of the proposed circuit with the literature

| Reversible multiplier             | Calculations           | NoG |

|-----------------------------------|------------------------|-----|

| The proposed design               | 16(PG)+8(PFAG)+4(PG)   | 28  |

| Reference [12]<br>(second design) | (9TG+7PG)+ 8PFAG+4PG   | 28  |

| Reference [12]<br>(first design)  | (9TG+7PG)+8HNG +4PG    | 28  |

| Reference [11]                    | (16PG+16FG)+8PFAG+4PG  | 44  |

| Reference [7]                     | (16PG+16FG)+8HNG+4PG   | 44  |

| Reference [10]                    | (16PG+16FG)+12MKG      | 44  |

| Reference [9]                     | (16FRG+16FG)+13TSG     | 45  |

| Reference [8]                     | (16FRG+16FG)+12NG+12TG | 56  |

**TABLE 3.** Comparison of garbage outputs (Gout) of the proposed circuit with the compared circuits

| Reversible multiplier          | Gout |

|--------------------------------|------|

| The proposed design            | 28   |

| Reference [12] (second design) | 28   |

| Reference [12] (first design)  | 28   |

| Reference [11]                 | 52   |

| Reference [7]                  | 52   |

| Reference [10]                 | 56   |

| Reference [9]                  | 58   |

| Reference [8]                  | 56   |

**TABLE 4.** Comparison of quantum costs (QC) and total costs (TC) of the proposed circuit with the literature

| Reversible<br>multiplier          | Calculations                                             | QC  | TC  |

|-----------------------------------|----------------------------------------------------------|-----|-----|

| The proposed design               | $(16\times4)(\text{for PG})+(8\times6)$ (for PFAG)+(4×4) | 128 | 184 |

| Reference [12]<br>(second design) | (9×5)(for TG)+(16×1)+(11×4)<br>(for PG)+(8×8)(for PFAG)  | 153 | 209 |

| Reference [12]<br>(first design)  | (9×5)(for TG)+(16×1)+(11×4)<br>(for PG)+(8×6)(for HNG)   | 137 | 193 |

| Reference [11]                    | (16×5)+(16×1)+(4×4)+(8×8)                                | 160 | 256 |

| Reference [7]                     | (16×5)+(16×1)+(4×4)+(8×8)                                | 160 | 256 |

| Reference [10]                    | (16×4)+(16×1)+(12×13)                                    | 236 | 336 |

| Reference [9]                     | (16×5)+(16×1)+(13×14)                                    | 278 | 381 |

| Reference [8]                     | (16×5)+(16×1)+(12×7)+(12×5)                              | 220 | 332 |

**4. 4. Circuit Depth** Depth of circuits (D) is one of the other main factors in designing a reversible logic circuit. The circuit depths of the compared designs are shown in Table 5.

**4.5. Constant Garbage Input** Number of constant garbage inputs (Gin) is one of the other main factors in designing a reversible logic circuit. For the compared designs, garbage inputs are shown in Table 6.

**4. 6. Circuit Cost** One of the factors of hardware complexity of reversible circuits is the number of XOR, AND, NOT logic in the output expressions which are defined as:

- a = calculation of a two input XOR gate.

- b = calculation of a two input AND gate.

- d = calculation of a NOT gate.

The circuit costs (CC) (sometimes called total logic calculations or complexity) of the compared designs are shown in Table 7.

**TABLE 5.** Comparison of depths (D) of the proposed circuit with the literature

| Reversible<br>multiplier          | Calculations                                                | D  |

|-----------------------------------|-------------------------------------------------------------|----|

| The proposed design               | 2(for PG)+(4+4)(for PFAGs) +2(for<br>PG)+(4+4+4)(for PFAGs) | 24 |

| Reference [12]<br>(second design) | 2(for TG and PG) + 2(for PG) + (4×4)<br>+ (2×4)             | 28 |

| Reference [12]<br>(first design)  | 2(for TG and PG) + 2(for PG) + (4×4)<br>+ (2×4)             | 28 |

| Reference [11]                    | 2(for FG)+2(for PG)+ 2(for<br>PG)+(2×4)+(4×4)(for PFAG)     | 30 |

| Reference [7]                     | 2(for FG)+2(for PG)+ 2(for PG)<br>+(2×4)+(4×4)(for HNG)     | 30 |

| Reference [10]                    | 2(for FG)+2(for PG)+(7×5)<br>(for MKG)                      | 39 |

| Reference [9]                     | 2(for FG)+5(for FRG) +(7×5)(for TSG)                        | 42 |

| Reference [8]                     | 2(for FG)+5(for FRG ) +7(3+2)(for TG and NG)                | 42 |

**TABLE 6.** Comparison of garbage inputs (Gin) of the proposed circuit with the literature

| Reversible multiplier          | Gin      |

|--------------------------------|----------|

| The proposed design            | 28       |

| Reference [12] (second design) | 28       |

| Reference [12] (first design)  | 28       |

| Reference [11]                 | 28+16=44 |

| Reference [7]                  | 28+16=44 |

| Reference [10]                 | 32+16=48 |

| Reference [9]                  | 34+16=50 |

| Reference [8]                  | 31+16=47 |

**TABLE 7.** Comparison of circuit cost (CC) of the proposed circuit with the literature

| Reversible<br>multiplier          | Logic Calculations                                                                    | СС            |

|-----------------------------------|---------------------------------------------------------------------------------------|---------------|

| The proposed design               | 16×(2a+1b)(for PG)+<br>8×(5a+2b)(for PFAG) +<br>4×(2a+1b)(for PG)                     | 80a+36b       |

| Reference [12]<br>(second design) | 9×(1a+1b)(for TG)+<br>7×(2a+1b)(for PG)+<br>8×(5a+2b)(for PFAG)+<br>4×(2a+1b)(for PG) | 71a+36b       |

| Reference [12]<br>(first design)  | 9×(1a+1b)(for TG)+<br>7×(2a+1b)(for PG)+<br>8×(5a+2b)(for HNG)+<br>4×(2a+1b)(for PG)  | 71a+36b       |

| Reference [11]                    | (80+16)a+36b                                                                          | 96a+36b       |

| Reference [7]                     | (80+16)a+36b                                                                          | 96a+36b       |

| Reference [10]                    | (92+16)a+52b+36d                                                                      | 108a+52b+36d  |

| Reference [9]                     | (110+16)a+103b+71d                                                                    | 126a+103b+71d |

| Reference [8]                     | (80+16)a+100b+68d                                                                     | 96a+100b+68d  |

#### **5. DISCUSSION**

The quantum parameters of different multiplier circuits are shown in Table 8. Regarding to the previous multiplier circuits in [7-12], all quantum parameters of the proposed design is improved. However, in term of the number of reversible logic gates, garbage output and input, the proposed multiplier shows the same value as the multiplier circuit in [12].

In term of quantum cost and depth, our proposed circuit is the best, because of using the CSA in RPA part, and replacing the Toffoli gates with Peres gates in PPGC part of the original circuit [12]. On the other hand, the circuit cost of the proposed circuit is slightly worse than the reference [12], but at the same time, the total cost of the proposed circuit is the best.

#### 6. CONCLUSSION

Reversible logic circuits are of particular interest in low power CMOS design, optical computing, DNA computing, bioinformatics, quantum computing and nanotechnology. Multiplier is a basic arithmetic cell in computer arithmetic units. Furthermore, reversible implementation of this unit is necessary for quantum computers. Targeting this purpose, various designs can be found in the literature.

This paper introduces a novel 4×4 reversible multiplier circuit. The advanced design is based on the same gates (PGs only) that it is easy to implement. In addition, use of PGs in PPGC part improves the quantum cost of the proposed design without needing to any duplicating gates. Furthermore, using CSA technique in RPA part reduces the circuit depth of the proposed design.

| Reversible<br>multiplier          | CC            | NoG | Gout | Gin | QC  | ТС  | D  |

|-----------------------------------|---------------|-----|------|-----|-----|-----|----|

| The proposed design               | 80a+36b       | 28  | 28   | 28  | 128 | 184 | 24 |

| Reference [12]<br>(second design) | 71a+36b       | 28  | 28   | 28  | 153 | 209 | 28 |

| Reference [12]<br>(first design)  | 71a+36b       | 28  | 28   | 28  | 137 | 193 | 28 |

| Reference [11]                    | 96a+36b       | 44  | 52   | 44  | 160 | 256 | 30 |

| Reference [7]                     | 96a+36b       | 44  | 52   | 44  | 160 | 256 | 30 |

| Reference [10]                    | 108a+52b+36d  | 44  | 56   | 48  | 236 | 336 | 39 |

| Reference [9]                     | 126a+103b+71d | 45  | 58   | 50  | 278 | 381 | 42 |

| Reference [8]                     | 96a+100b+68d  | 56  | 56   | 47  | 220 | 332 | 42 |

**TABLE 8.** Comparison of different reversible multiplier circuits (a,b and c: number of XOR, AND, and NOT gates, respectively, CC:Circuit Cost, NoG:Number of Gate, Gout:Garbage output, Gin:Garbage input, QC:Quantum Cost, TC:Total Cost, D:Depth)

Regarding to the best previous design, the proposed reversible multiplier decreases the quantum cost, total cost and depth, without increasing in the number of gate, number of garbage input and outputs. However, the circuit cost is increased slightly regarding to the best previous design.

As future works, some other reversible implementation of more complex arithmetic circuits such as function evaluations and multiplicative division circuits can be investigated using the proposed multiplier.

#### 7. REFERENCES

- 1. Landuer, R., "Irreversibility and heat generation in the computing process", *IBM Journal of Research and Development*, Vol. 5, (1961), 183-191.

- Demmer, M., Fonseca, R. and Koushanfa, F., "Richard Feynman: Simulating physics with computers", *International Journal of Theoretical Physics*, Vol. 21, No. 6-7, (1982), 467-488.

- Bennet, C.H., "Logical reversibility of computation", *IBM* Journal of Research and Development, Vol. 17, No. 6, (1973), 525-532.

- Nielson, M. and Chuang, I., "Quantum Computation and Quantum Information", Cambridge University Press, (2002).

- Thapliyal, H. and Srinivas, M. B., "Novel reversible TSG gate and its application for designing reversible carry look ahead adder and other adder architectures", *Proceedings of 10<sup>th</sup> Asia-Pacific Computer Systems Architecture Conference*, (2005), 775-786.

- Haghparast, M. and Navi, K., "A Novel Reversible Full Adder Circuit for Nanotechnology Based Systems", *Journal of Applied Science*, Vol. 7, No. 24, (2007), 3995-4000.

- Haghparast, M., Jafarali Jassbi, S., Navi, K. and Hashemipour, O., "Design of a novel reversible multiplier circuit using HNG gate in nanotechnology", *World Applied Sciences Journal*, Vol. 3, No. 6, (2008), 974-978.

- Thaplyal, H., Srinivas, M. B. and Arabnia, H. R., "A reversible version of 4×4 bit array multiplier with minimum gates and garbage outputs", *International Conference on Embedded System and Applications* (ESA'05), Las Vegag, USA, (2005), 106-114.

- 9. Thaplyal, H. and Srinivas, M. B., "Novel reversible multiplier architecture using reversible TSG gate", *IEEE International Conference on Computer Systems and Applications*, (2006), 100-103.

- Shams, M., Haghparast, M., Navi, K., "Novel reversible multiplier circuit in nanotechnology", *World Applied Science Journal*, Vol. 3, No. 5, (2008), 806-810.

- Islam, M. S., Rahman, M. M., Begum, Z. and Hafiz, M. Z., "Low cost quantum realization of reversible multiplier circuit", *Information Technology Journal*, Vol. 8, No. 2, (2009), 208-213.

- 12. Mohammadi, M., Navi, K. and Eshghi, M., "Optimized reversible multiplier circuit", *Journal of Circuits, Systems and Computers*, Vol. 18, No. 2, (2009), 311-323.

- 13. Ehsanpour, M., Moallem, P., Vafaei, A., "Design of a Novel Reversible Multiplier Circuit Using Modified Full Adder", 2010 International Conference on Computer Design and Applications, Vol. 3 ,(2010), 230-234.

- Feynman, R. P., "Quantum mechanical computers", *Optical News*, Vol. 11, No. 2, (1985), 11-20.

- Toffoli, T., "Reversible computing", In Automata, Lnaguages and Programming, Spring-Verlog, (1985), 632-644.

- Fredkin, E., Toffoli, T., "Conservative logic", *International Journal of Theoretical Physics*, Vol. 21, No. 3-4, (1982), 219-253.

- Peres, A., "Reversible logic and quantum computers", *Physical Review A*, Vol. 32, No. 6, (1985), 3266-3276.

- 18. Azad Khan, M. H., "Design of full adder with reversible gate", International Conference on Computer and Information Technology, Dhaka, Bangladesh, (2005), 515-519.

- Banerjee, A., and Pathak, A., "An analysis of reversible multiplier circuits", arXiv preprint arXiv:0907.3357 (2009).

- 20. Naderpour, F. and Vafaei, A., "Reversible multiplier: Decreasing the depth of the circuit", 5<sup>th</sup> International Conference on Electrical and Computer Engineering (ICECE2008), Dhaka, Bangladesh, (2008), 306-310.

- 21. Zhou, R., Shi, Y., Cao, J. and Wang, H., "Comment on Design of a novel reversible multiplier circuit using HNG gate in nanotechnology", *World Appllied Science Journal*, Vol. 10, No. 2, (2010), 161-165.

- 22. Gupta, P., Agrawal, A. and Jha, N. K., "An Algorithm for synthesis of reversible logic circuits", *IEEE Transactions on Computer-aided Design of Integrated Circuits and Systems*, Vol. 25, No. 11, (2006), 2317-2330.

- Perkowski, M., Al Rabadi, A., Kerntopf, P., Buller, A., Chrzanowska-Jeske, M., Mishchenko, A., Azad Khan, M., Coppola, A., Yanushkevich, S., Shmerko, V. and Jozwiak, L., "A general decomposition for reversible logic", *In Reed-Muller Workshop*, (2001), 119-139.

- 24. Tayari, M. and Eshghi, M., "Design of 3-Input Reversible Programmable Logic Array", *Journal of Circuits, Systems and Computers*, Vol. 20, No. 2, (2011), 283-297.

- Maslov, D. and Dueck, G. W., "Garbage in reversible design of multiple output functions", *Proceeding of 6<sup>th</sup> International* Symposium on Representation and Metodology of future Computing, (2003), 162-170.

#### APPENDIX

An introduction to reversible logics and corresponding quantum parameters are presented in this appendix.

**1. Introduction to Reversible Logics** A reversible logic circuit comprises reversible gates. A gate that implements one to one mapping between n inputs and n outputs is called an  $n \times n$  reversible logic gate that can be represented as:

$$I_{v} = (x_{1}, x_{2}, ..., x_{n})$$

$$O_{v} = (y_{1}, y_{2}, ..., y_{n})$$

(1)

where  $I_V$  and  $O_V$  are the input and output vector.

The reversible logic gate must have the same number of inputs and outputs, and for each input pattern there must be a unique output pattern [3]. Reversible logic circuits avoid energy loss by "uncomputing" the computed information using recycling the energy in the system [3].

Synthesis of the quantum or reversible logic circuits in comparison to synthesis of the traditional irreversible

logic circuits has two restrictions that should be mentioned [23]:

- In the reversible logic, fan-out of any gate output is not allowed.

- Several authors assume that there should be no loops of gates and we followed this assumption in this paper.

Due to these restrictions, synthesis of the reversible circuits can be carried out from the inputs towards the outputs and vice versa [22]; so, there is a one-to-one mapping between input and output vector. In an *n*-output reversible gate, the output vectors are permutations of the numbers 0 to  $2^n$ -1.

**2. Parameters of Reversible Circuits** There are some important parameters in designing an efficient reversible logic circuits including: the number of gates (NoG), quantum cost (QC), number of garbage outputs (Gout), number of constant garbage inputs (Gin), circuit cost (CC) (which is sometimes called the total logic calculations or hardware complexity) and depth of reversible circuits (D).

The number of gates as one of the comparison parameters is used to evaluate the implementation cost. The quantum cost of a reversible circuit is the number of  $(1\times1)$  or  $(2\times2)$  reversible gates used to implement the circuit. These elementary quantum gates with quantum cost equal to one is defined as follows [4]:

- Inverter (NOT): A single qubit (basic unit of information in quantum computer) is inverted.

- Controlled NOT (CNOT): The target qubit is inverted if the control qubit is 1.

- Controlled V: Performs the V operation known as the square root of NOT, since two consecutive V operations are equivalent to an inversion.

- Controlled  $-V^+$ : Performs the inverse of V.

The circuit depth is defined as the number of steps required to execute all available gates in a circuit [24]. The garbage outputs must be added as necessary so that the output patterns are distinct, and it is not used for further computations. Of course, the constant garbage inputs must be added, as a necessity, to balance the number of inputs and outputs [25]. Reduction of these quantum parameters is the bulk of the work in reversible circuits design.

# A Novel Design of Reversible Multiplier Circuit

#### TEACHNICAL NOTE

چکيده

#### P. Moallem<sup>a</sup>, M. Ehsanpour<sup>b</sup>

<sup>a</sup> Department of Electrical Engineering, University of Isfahan, Isfahan, Iran. <sup>b</sup> Department of Computer, Falavarjan Branch, Islamic Azad University, Falavarjan, Isfahan, Iran

#### PAPER INFO

Paper history: Received 22 June 2012 Received in revised form 5 January 2013 Accepted 24 January 2013

Keywords: Reversible Circuit Reversible Multiplier Reversible Gate Quantum Parameters جمع کننده او ضرب کننده او بخش املی واحدهای محاسباتی سخت افزار کامپیوتر محسوب شده و نقش عمده ای در محاسبات برگشت پذیر ایفا می کنند. این مقاله، مدار ضرب کننده برگشت پذیر xx نوینی را معرفی میکند که در طراحی مدار مولد حاصلضرب های جزئی، تنها از دریچه های پرس استفاده کرده است و نیازی به دریچه های کپی ندارد. در ضرب کننده پیشنهادی، از دروازه برگشت پذیر تمام جمع کننده پرس بهینه شده، به همراه روش جمع با ذخیره نقلی، در قسمت جمع کننده موازی استفاده شده است. مقایسه ضرب کننده پرس بهینه شده، به همراه روش جمع با ذخیره نقلی، که پارامترهای کوانتومی بهبود یافته است. طرح پیشنهادی، کمترین مقدار هزینه کوانتومی و عمق را به کمک طراحی نوینی در قسمت مدار مولد حاصل ضربهای جزیی نشان می دهد. هزینه مداری طرح پیشنهادی با دیگر طرح ها نشان می دهد مقایسه اندکی افزایش یافته، اما از نقطه نظر هزینه کل که به صورت مجموع هزینه کوانتومی و هزینه مداری تعریف می شود، کمترین مقدار را نشان می دهد. علاوه بر این، در طرح پیشنهادی به نسبت بهترین طرح مورد می مواد، مقایری افاه و و رودی اضافه و و رودی اضافه می شود، کمترین مقدار را نشان می دهد. علاوه بر این، در طرح پیشنهادی، تعداد دریچه، خروجی اضافه و و رودی اضافه نسبت به بهترین طرح مورد مقایسه، افزایشی نیافته است. ضرب کننده پر منه به می ماری کر می و می را می می طرحی و مرد است.

doi: 10.5829/idosi.ije.2013.26.06c.03

585