### International Journal of Engineering

Journal Homepage: www.ije.ir

## A Novel Low Voltage, Low Power and High Gain Operational Amplifier Using Negative Resistance and Self Cascode Transistors

M. Fallah, H. Miar Naimi\*

Department of Electrical Engineering, Babol University of Technology, Iran

PAPER INFO

Paper history: Received 15 October 2012 Accepted in revised form 15 November 2012

Keywords: Negative Resistance Op Amp Self Cascode Transistors

#### A B S T R A C T

In this work, a low power, low voltage and high gain operational amplifier is proposed. For this purpose, a negative resistance structure is used in parallel with output to improve the achievable gain. Because of using self cascode transistors in the output, the proposed structure remains approximately constant in a relatively large output voltage swing causing an invariable gain. To evaluate the proposed method an op amp was designed in 0.18µm CMOS technology. The simulation results showed a gain of 84dB, unity gain bandwidth of 12.45MHz and phase margin of 81 degree; with 1V power supply and 1pF load capacitor.

doi: 10.5829/idosi.ije.2013.26.03c.10

#### 1. INTRODUCTION

Growing microelectronics industry and emerging short channel CMOS process forced circuit designer to design circuits with higher speed, lower voltage supply and power consumption [1-3]. On the other hand with the advent of electronic equipment in daily life, low power and low voltage along with higher performance designs caught the attention of designers. Unfortunately, the threshold voltage of CMOS transistors hasn't scaled down proportional to the technology [4], so the low voltage design remains a challenging area in the circuit design context [5, 6]. Op amps are one of the key elements in electronics circuits such as filters and A/D (D/A) convertors [7, 8]. In these applications, the high gain of op amps plays a critical role on the performance of the circuits so designing high gain and low voltage op amps is a challenging task for designers [9].

A few techniques have been proposed for increasing the gain of op amps like cascoding transistors that increases the output resistance [10]. However, this technique lowers output swing, so it cannot be considered in low voltage designs. Cascade stages is another approach to increase the gain but these

structures usually need compensation circuit and are highly power consuming and low speed [11]. Gain boosting is another technique that like cascade stages have usually low speed [12].

Another approach for op amp gain enhancement is to use parallel negative resistance network at the output stage to increase the equivalent output resistance. There are a few works using this technique mainly because the negative resistance varies with output swing and the circuit loses its performance [13-17]. In this work, the cross coupled pair is used and directly connected to the output as the negative resistance, so no new node is added and the speed isn't degraded so much. Indeed without degrading the speed the gain is increased significantly.

As mentioned before, the main drawback of this technique is the dependency of to the negative resistance to the output swing. To overcome this problem, we introduce a new negative resistance network that is approximately independent to the output swing and holds its good features for large swings as well. The mentioned technique employs self cascode transistors. The rest of the paper is as follows, in section 2, typical op amps are studied and in section 3 the cross coupled pair generating negative resistance is introduced. In section 4, the cascode transistor based negative resistance is described. Section 5, shows the

<sup>\*</sup>Corresponding Author Email: <u>H Miare@nit.ac.ir</u> (H. Miar Naimi)

simulation results and discussions and finally section 6 concludes the paper.

#### 2. TYPICAL OP AMPS

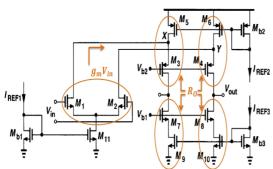

In the folded cascode op amps (Figure 1) the input differential pair converts the input voltage to current signal. The current signal is directed to the output node with high output resistance and generates the high amplitude output voltage signal.

The gain can be expressed as Equation (1):

$$\begin{aligned} \left| A_{V} \right| &= G_{m} R_{out} , G_{m} \approx g_{m1} \\ R_{out} \approx & \left[ \left( g_{m3} + g_{mb3} \right) r_{o3} \left( r_{o1} - r_{o5} \right) \right] \left[ \left( g_{m7} + g_{mb7} \right) r_{o7} r_{o9} \right] \\ \left| A_{V} \right| \approx & g_{m1} \left\{ \left[ \left( g_{m3} + g_{mb3} \right) r_{o3} \left( r_{o1} - r_{o5} \right) \right] \right. \end{aligned}$$

$$\left. \left( 1 + \left( g_{m7} + g_{mb7} \right) r_{o7} r_{o9} \right] \right\}$$

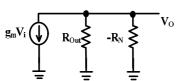

where,  $r_{oi}$  and  $g_{mi}$  are the output resistance and transconductance of the i-th transistor. Equation (1) indicates that increasing the output resistance increases the op amp overall gain. To do this we can parallel a negative resistor with the output node as shown in Figure 2. Hence, Equation (2) can be written for the op amp gain.

$$\left| A_{V,new} \right| = G_m R_{out,new} \tag{2}$$

where,  $R_{out,new}$  is the output resistance in the Figure 2. If we consider  $R_N = R_{out} + \Delta R_{out}$  we have:

$$R_{out,new} = R_{out} \quad \left(-R_N\right) = R_{out} + \frac{\left(R_{out}\right)^2}{\Delta R_{out}} \tag{3}$$

**Figure 1.** Folded cascade op amp and the simple voltage amplification mechanism.

Figure 2. Op amp output node paralleled with a negative resistance.

As shown in Equation (3), small  $\Delta R_{out}$  causes  $R_{out,new}$  to be very larger than  $R_{out}$  so the new overall gain will be very larger than the former.

The key point here is that  $\Delta R_{out}$  should be kept constant over output large swing. In section 3, we show that the traditional negative resistances behave well only over a small voltage interval then we will introduce a novel negative resistance with constant value over a large voltage swing.

### 3. THE PROPOSED OP AMP AND NEGATIVE RESISTANCE GENERATOR

One stage op amp with self cascode transistors topology is chosen for its low power consumption and power supply. As mentioned before, to increase the op amp gain we parallel a negative resistance to the output.

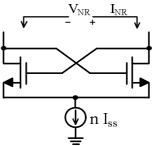

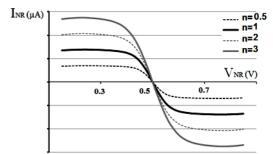

A simple cross coupled pair generating negative resistance is shown in Figure 3. The current-voltage curve of cross coupled pair is shown in Figure 4.

In Figure 4, the tail current for the curve with label n is n-times of the tail current for the curve with label 1. As shown in Figure 4, the cross coupled pair shows a negative resistance for a narrow voltage. Another key point here is that the curves slope (i.e. the negative resistance), would not remain constant with  $V_{\rm NR}$  variations. This will result in the degradation of the negative circuit role for gain enhancement.

Figure 3. The negative resistance network.

**Figure 4.** The current-voltage curve of circuit in Figure 3.

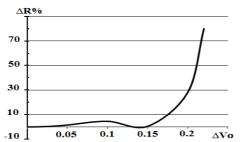

Figure 5 shows the negative resistance variations with the output swing. As shown in Figure 5, the negative resistance is constant for a limited output voltage interval (only about 0.2 V) which is not the same as output swing (rail to rail swing). To overcome this problem, we propose a new structure in which the voltage variation over the cross coupled transistors is very small in contrary to the output large swings. In fact, instead of putting the negative resistance directly at the output we use self cascode transistors and put the negative resistance at the drain of the second transistor.

#### 4. SELF CASCODE TRANSISTORS

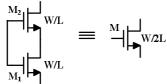

Using self cascode transistors is an approach that is used in low voltage designs. Figure 6 shows the mentioned transistors and their equivalent. In the Figure 6, gates of M1 and M2 are connected together. Using this combination increases the output resistance without considerably limiting its achievable swing. If both transistors in the Figure 6 have the same aspect ratio then the combinations is equivalent to a transistor with length of twice of each transistor. This means that the output resistance of this structure is more than a single transistor. The size of M1 is usually chosen much greater than M2. This will reduce the variations of V<sub>OD1</sub>, because in this case the  $r_{ds1}$  to output resistance ratio decreases. This causes a small ratio of the output voltage swing put at the V<sub>DS1</sub>. To improve the output resistance we put the negative resistance at the drain of M1 as shown in Figure 7. The  $V_{D1}$  to  $V_{D2}$  can be written as (4).

$$\frac{V_{D1}}{V_{D2}} = \frac{r_{ds1}}{r_{ds1} \left(1 + g_{m2} r_{ds2}\right) + r_{ds2}} \tag{4}$$

**Figure 5.** Negative resistance variations versus the output swing.

Figure 6. Self cascode transistors and the equivalent transistor

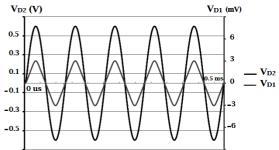

**Figure 7.** The variations of  $V_{D1}$  with respect to the output swing.

In Equation 4,  $r_{ds1}$  is the drain-source resistance of M1 in the triode region and  $r_{ds2}$  and  $g_{m2}$  are the drain-source resistance and transconductance of M2 in saturation region. Obviously, to decrease Equation 4, we should decrease  $r_{ds1}$  as much as possible. Regarding the relation between  $r_{ds1}$  and  $V_{D1}$ , we should decrease  $V_{D1}$  to an appropriate level. If  $r_{ds1}$  is chosen very small, then the tail current of the negative resistance network would have a great value.

Figure 7 shows the variations of  $V_{\rm D1}$  with respect to the output swing. In Figure 7, for a 0.6V output swing  $V_{\rm D1}$  experiences a 3 mV variation for which the negative resistance can be considered constant. Putting the negative resistance here provides us a large and constant output resistance over a large output voltage swing. Using this technique, we are now able to design a low voltage and high gain op amp. The designed op amp is discussed in section 5.

#### 5. THE DESIGNED OP AMP

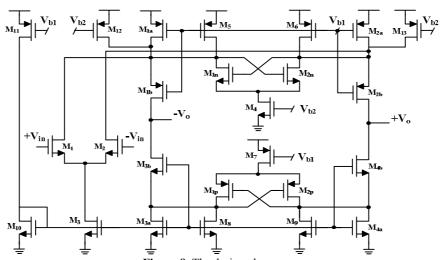

We use the telescopic topology with the minimum stages as the base structure of the designed op amp. The final structure is shown in Figure 8.

In the designed op amp shown in Figure 8,  $M_{1a}$ ,  $M_{2a}$ ,  $M_{3a}$  and  $M_{4a}$ , all are in the triode region, having a small drain to source resistance. So, to increase the equivalent resistor we need to parallel a small negative resistance with these transistors. For small negative resistance, cross coupled pair should be biased with a high tail current that is somehow a problem. To solve this problem we reduce the current of Mia using some additional transistor in parallel to those that leads to higher drain-source resistor.  $M_{12}$  and  $M_{13}$  are the auxiliary transistors that are added to the circuit to increase the resistance at the drain of input transistors. This causes the major input current signal to direct to the output node and consequently the op amp overall gain is improved.

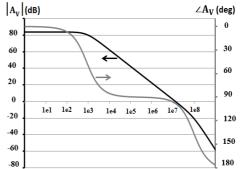

In the bode diagram,  $A_v = \Delta V_o(f)/\Delta V_{in}(f)$  shown in Figure 9, it can be find out that with a proper design we

can obtain very high gain with a 1V DC supply. In addition, regarding to the simple structure of the op amp, there is no need to add compensation circuit.

The output swing is  $V_{\rm DD}$ - $2V_{\rm od}$ . Note that in the same bias current, self cascode transistors approximately need the same overdrive voltage as a single transistor. So, without restricting the output swing the proposed op amp shows a very higher gain.

The op amp specifications are compared to the other works in Table 1.

#### 6. CONCLUSIONS

In this work a novel low voltage and high gain op- amp is proposed using self cascode transistors. The key point here is the high resistance at the output that remains constant over the whole output swing area. Because of minimum stacking stages used in this work, other specifications such as output swing, circuit speed and power consumption are better or at least comparable to the previous works.

Figure 9. The bode diagram of overall gain of op amp.

Figure 8. The designed op amp.

**TABLE 1.** The comparison of proposed op amp specifications with other works.

|                                      | Proposed op amp            | [4]       | [18] | [19] | [20] |

|--------------------------------------|----------------------------|-----------|------|------|------|

| Power supply (V)                     | 1                          | 0.6       | 0.8  | 0.8  | 0.9  |

| Open loop gain (dB)                  | 84                         | 73.5      | 60   | 49   | 62   |

| Unit gain frequency (MHz)            | 12.45                      | 0.013     | 0.6  | 69.2 | 0.54 |

| Phase margin (Degree)                | 81                         | 54.1      | 58   | 42   | 52   |

| Maximum Signal swing (V)             | $\pm (0.07 \text{-} 0.93)$ | 0.04-0.56 | 0.6  | R-R  |      |

| Slew rate (V/µSec)                   | 9.7                        | 0.0147    | 0.75 | 9.6  | 0.23 |

| CMRR (dB)                            | 62.3                       | 67.4      | 63   | 89.6 | 129  |

| PSRR (dB)                            | 74                         | 58.1      | 58   | 57.4 | 76   |

| Power consumption (µW)               | 85                         | 0.55      | 54.5 | 28.6 | 9.9  |

| Input Voltage noise $(nV/\sqrt{Hz})$ | 645@1KHz                   | 290@1KHz  |      |      |      |

#### 7. REFERENCES

- Chae, Y. and Han, G., "Low voltage, low power, inverter-based switched-capacitor delta-sigma modulator", *IEEE Journal of Solid-State Circuits*, Vol. 44, No. 2, (2009), 458-472.

- Song, J. Y. and Kwon, O. K., "Low-Power 10-Gb/s Transmitter for High-Speed Graphic DRAMs Using 0.18 um CMOS Technology", *IEEE Transactions on Circuits and Systems II*, Vol. 58, No. 12, (2011).

- Balankutty, A. and Kinget, P. R., "An Ultra-Low Voltage, Low-Noise, High Linearity 900-MHz Receiver With Digitally Calibrated In-Band Feed-Forward Interferer Cancellation in 65-nm CMOS", *IEEE Journal of Solid-State Circuits*, Vol. 46, No. 10, (2011), 2268-2283.

- Ferreira, L. H. C., Pimenta, T. C. and Moreno, R. L., "An ultralow-voltage ultra-low-power CMOS miller OTA with rail-to-rail input/output swing", *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol. 54, No. 10, (2007), 843-847.

- Shouli, Y. and Sanchez-Sinencio, E., "Low voltage analog circuit design techniques: A tutorial", *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, Vol. 83, No. 2, (2000), 179-196.

- Rajput, S. and Jamuar, S., "Low voltage analog circuit design techniques", *Circuits and Systems Magazine*, *IEEE*, Vol. 2, No. 1, (2002), 24-42.

- Kim, Y. J., Choi, H. C., Ahn, G. C. and Lee, S. H., "A 12 bit 50 MS/s CMOS Nyquist A/D converter with a fully differential class-AB switched op-amp", *Journal of Solid-State Circuits*, *IEEE*, Vol. 45, No. 3, (2010), 620-628.

- Thyagarajan, S. V., Pavan, S. and Sankar, P., "Active-RC Filters Using the Gm-Assisted OTA-RC Technique", *IEEE Journal of Solid-State Circuits*, Vol. 46, No. 7, (2011), 1522-1533.

- Liu, A. and Yang, H., "Low voltage low power class-AB OTA with negative resistance load", in Communications, Circuits and Systems Proceedings, International Conference on, IEEE. Vol. 4, (2006), 2251-2254.

- Alizadeh, B. and Dadashi, A., "An enhanced Folded Cascode op-amp in 0.18 μm CMOS process with 67dB dc-gain", in Faible Tension Faible Consommation (FTFC), IEEE, (2011), 87-90.

- Rahim, S. and Azmi, I., "A CMOS single stage fully differential folded cascode amplifier employing gain boosting technique", in Integrated Circuits (ISIC), 13th International Symposium on, IEEE, (2011), 234-237.

- Ahmadi, M. M., "A new modeling and optimization of gain-boosted cascode amplifier for high-speed and low-voltage applications", *IEEE Transactions on Circuits and Systems II:* Express Briefs, Vol. 53, No. 3, (2006), 169-173.

- Yan, J. and Geiger, R. L., "A high gain CMOS operational amplifier with negative conductance gain enhancement", in Custom Integrated Circuits Conference, Proceedings of the IEEE, (2002), 337-340.

- Allstot, D. J., "A precision variable-supply CMOS comparator", *IEEE Journal of Solid-State Circuits*, Vol. 17, No. 6, (1982), 1080-1087.

- Roubik, G., "Introduction to CMOS op-amps and comparators", *John Willy & Sons Inc*, Vol. 189, (1999).

- Nauta, B. and Seevinck, E., "Linear CMOS transconductance element for VHF filters", *Electronics letters*, Vol. 25, No. 7, (1989), 448-450.

- Nauta, B., "A CMOS transconductance-C filter technique for very high frequencies", *IEEE Journal of Solid-State Circuits*, Vol. 27, No. 2, (1992), 142-153.

- Haga, Y., Morling, R. C. S. and Kale, I., "A new bulk-driven input stage design for sub 1-volt CMOS op-amps", in Circuits and Systems, (ISCAS) Proceedings, International Symposium on, IEEE, (2006), 4-8

- Sehgal, R., Rajput, S. and Jamuar, S., "A 0.8 V operational amplifier using Floating Gate MOS technology", in Semiconductor Electronics, ICSE'06, International Conference on, IEEE, (2006), 795-799.

- Pan, S. W., Chuang, C. C., Yang, C. H. and Lai, Y. S., "A novel OTA with dual bulk-driven input stage", in Circuits and Systems, (ISCAS) International Symposium on, IEEE, (2009), 2721-2724.

# A Novel Low Voltage, Low Power and High Gain Operational Amplifier Using Negative Resistance and Self Cascode Transistors

M. Fallah, H. Miar Naimi

Department of Electrical Engineering, Babol University of Technology, Iran

چكىدە PAPER INFO

Paper history: Received 15 October 2012 Accepted in revised form 15 November 2012

Keywords: Negative Resistance Op Amp Self Cascode Transistors در کار ارائه شده، ساختاری از تقویت کنندهٔ عملیاتی با بهرهٔ بالا و توان پایین بهمراه منبع تغذیه پایین معرفی شده است. برای دستیابی به ویژگی های گفته شده با اتصال موازی ساختار مدار مقاومت منفی در خروجی آپ امپ، بهرهٔ مدار بطور قابل توجهی افزایش می یابد. همچنین با استفاده از ساختار ترانزیستورهای Self cascode در خروجی آپ امپ پیشنهادی، بهبود بهره با وجود تغییرات زیاد ولتاژ در خروجی همچنان برقرار است. برای ارزیابی روش پیشنهادی از طراحی آپ امپ در تکنولوژی CMOS 0.18 µm استفاده شده که شبیه سازی ها بهرهٔ 84 dB، پهنای باند بهرهٔ واحد 12.45 MHz و حاشیهٔ فاز ۸۱ درجه را با منبع تغذیهٔ ۱۷ و خازن خروجی 1 و انشان داد.

doi: 10.5829/idosi.ije.2013.26.03c.10