# MODELLING AND PERFORMANCE EVALUATION OF MULTI-PROCESSORS ORGANISATION WITH SHARED MEMORIES

### M. Naderi

Department of Electrical Engineering Tehran University of Science and Technology, Tehran, Iran

Received April 1987

**Abstract** This paper is primarily concerned with theoretical evaluation of the performance of multi-processors system. A markovian waiting line model has been developed for various different multi-processors configurations, with shared memory. The system is analysed at the request level rather than job level.

چگیده بحث املی مقاله حاضر در مــورد بررسی و تجزیه و تحلیل تئوری رفتار و عکسالعمل سیستم هــای کامپیوتری است که شامل چندین پردازشکر میباشند ، مدل ریاضی برای چندین نوع از این تشکیلات با حافظه مشترک براساس صفوف انتظار در حالت Markovian تهیه و استخراج گردیده است . در تهیه مدلهای ریاضی اساس تجزیه و تحلیل بر پایه درخواستهای ورود بحافظه بجای حجم عملیات اجرایی در سیستم کامپیوتری در نظر گرفته شده است .

Modelling and Performance Evaluation of Multi-Processors Organisation.

Thirty years ago the designer designed his systems out of circuit level components such as resistors, diodes and transistors. Later, switching circuit level components which are represented by gates and flip-flops, became available as SSI components. With the introduction of medium scale integration (MSI) register transfer level components appeared as well as arithmetic and logic units, registers, etc. The advent of large scale integration (LSI) has made memories and, even processors, primitive components from which systems are designed.

VLSI as microprocessors have had a dramatic impact on applications that require minor adjustments. They have been used for instruments, industrial controllers, intelligent terminals, and communication systems as special function processors in large computers and multi-micro-networks.

The question naturally arises as to whether the microprocessor, which has proved so successful in these diverse applications, can be used as a building block for large general purpose computer networks. In other words, can a suitably interconnected set of microprocessors be used for tasks that currently require large uniprocessor capable of executing millions of instruction per second?

At present there is no definitive answer to this question, but there are several reasons to believe that multiple-microprocessor systems might indeed be viable. Following this belief one can think about how one can connect several of these processors and memories together and what is the effectiveness of the organisations. Finally, how can one measure or evaluate the performance parameters of such an organisation.

Throughout this paper an attempt is made to provide resonable answers to some of the above questions through a mathematical waiting line model approach. A method of investigation is proposed to evaluate the performance of a large scale multi-processors as a sophisticated tool for decreasing the financial risk involved in developing a network of large organisation.

The objectives of this investigation are:

- 1: The ability to model existing and proposed multiprocessors.

- 2: The ability to compare different multiprocessor organisations, through system performance.

- 3: To provide a facility (tool) with which one can easily create and try out new multiprocessor systems, tailored to a particular application

- 4: To enable one to measure the performance parameters of available multi-processor organisations.

## Performance Evaluation of Multi-Processors Organisation.

The following statistical problem arises in the study of many computer organisations. memory unit is required to attend to a number of processors and I/O units which request memory from time to time. Each time a unit (processor or I/O) makes a request, the memory unit organisation has to do a certain amount of decision-making and testing before it can be restarted to give a service to that unit. If a unit makes a request while the memory is on communication mode with another unit, the second unit must wait until the memory finishes with the first one. A waiting line or queue occurs in any multicomputer organisation. When, at a given time, the number of requests desiring service (from memory or any resources) exceeds the capacity of the service facility.

The problem is to estimate the effect of

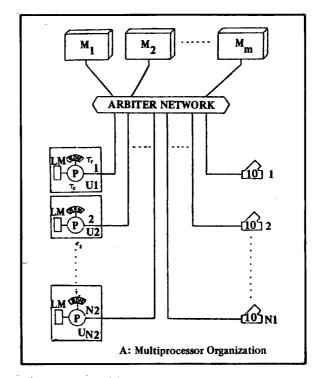

interference on throughput and efficiency, the time taken to give service to a request and the number of waiting units for a shared memory in multi-processor organisations. We are interested in applying a waiting line model in such organisations which is shown in figure 1. In such an organisation each microprocessor or I/O unit apply a request for a shared memory unit.

Figure 1. Multi-processors organization.

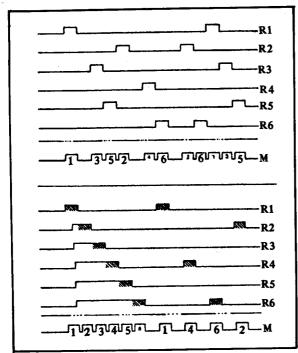

All such situations may be described by mathematical models which we term Finite Request Source Waiting Line Modles and define as waiting line models in which the request for use of memory emanates from N units (processors and I/O, s). In figure 2 it shows how several units made a request for a memory unit and how the memory unit gave service to them, one by one, in the order of first come, first served (FCFS).

If a processor or I/O unit makes a request it will be immediately attended to by the memory if the memory unit is free, but if the unit makes a request while the memory is busy with another unit it has to wait until the memory becomes free. This results in a loss of efficiency which is said to arise due to interference. Obviously, if the number units assigned to the one memory system becomes large, the loss of efficiency due to the interference increases. On the other hand, if fewer processor and I/O units are assigned to the one shared memory (or any resources) the price per performance increases. Hence, the problem is to determine the number of units to be assigned to a memory in order to minimize output costs by balancing the cost of the memory system against the loss of efficiency due to multi-processor organisations.

Figure 2. Time diagram for multi-processors organization.

Markovian Waiting Line Model Organisation for Multi-Processors System

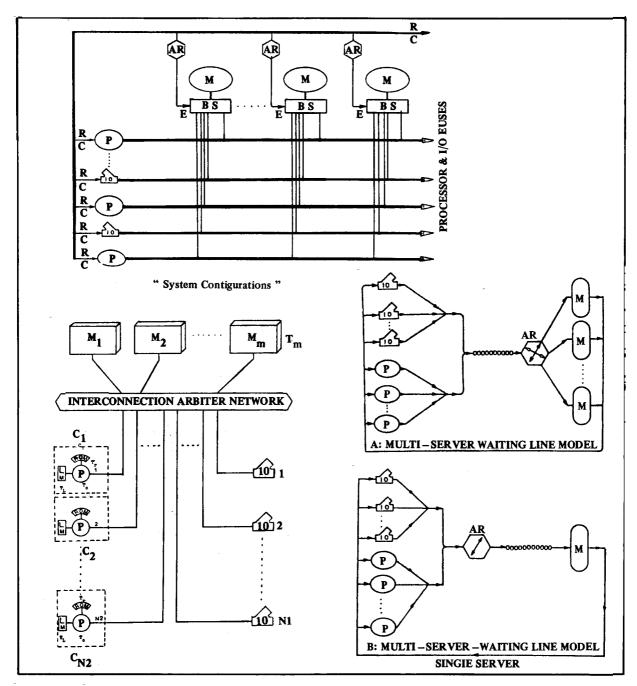

We now consider a subsystem (figure-3) of

multi-processor organisations with N2 processors and N1 I/O, S. Each processor has a local or private memory which communicates with it. As far as it can satisfy all requirements, if no desirable instruction or data at local memory can be found, the processor makes a request to communicate with the main memory unit. The effect of I/O units activity will not be modelled explicitly, the I/O is an I/O processor. Thus, from the main memory point of view, the I/O channel is logically equivalent to the other processors.

Since all units function independently, it follows that the probability of occurrence of a request is proportional to the total number of units i.e., N= N1 + N2, functioning at a given instant. The mean frequency of arrival requents in the system is a function of the number of waiting units in the queue under the service, i.e., n. In order to simplify the calculations, it is assumed that R is the mean arrival request frequency per unit of time so that when all N units are running independently of the main memory or in case of I/O units being idle.

In the most common stochastic queuing models it is assumed that inter-arrival request times and service or communcation times obey the exponential distribution or, equivalently, that the arrival rate of request (R) and service rate (S) follow a poisson distribution.

In subsystem organisations under these conditions and assumptions, the probability that a request can occur between time (t) and time (t + dt) is equal to: (N-n) Rdt + O(dt) The probability of service completion in(dt) is:

$$Sdt + O(dt)$$

and the probability of more than one request (R) more than one service completion (s) in(dt) is infinitesimal and will be O(dt)

Figure 3. Multi Micro Processors Organization and Waiting line Models

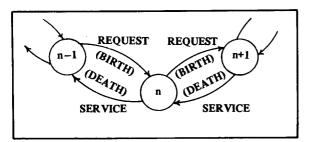

We have, then, a process with requests and services occurring randomly over time, with the probability mechanism just described. Request arrivals can be considered as "BIRTHS" to the system. Since, if the queue system is in state n (we consider system state as the number of waiting units in the system) and a

new request occurs, the state is changed to (n+1).

On the other hand, a services completion occurring while the system is in state (n) sends the system down one to a state of (n-1) and can be looked upon as a "DEATH". This type of process is often referred to as a

"BIRTH-DEATH" process, or markov processes with stationary transition and countable state space.

The possible states transition of Markovian chainor birth and death processes is shown in figure 4.

Figure 4. State Transition of markovian feeqss

According to the Chapman-Kolmogrov euation, the probability that there are (n) units in the system at some selected moment is the sum of probabilities associated with the state changes leading to state n.

$$P_{n}(t+dt) = \sum_{m} P_{m}(t) \cdot P_{mn}(dt) \qquad (1)$$

where

$P_m(t) = \text{prob.}$  system in state m at time t

$P_{mn}(dt) = prob.$  { transition from state m to state n in dt/system in state m at time t }.

In the markov process we shall permit direct transitions from any state (m) to any state (n). The transition probabilities are permitted to vary in time. But in our case, we have already seen the direct transition from a state n is possible only to the neighbouring states (n+1) or (n-1); (the poisson process property).

Thus in such a case, we have:

$$P_n(t+dt) = \sum_{m=n-1}^{n+1} P_m(t) \cdot P_{mn}(dt)$$

(2)

since  $P_{mn}(dt) = 0$  for m < n-1 and m > n+1.

an with arrival request (R) and service rate (S) both independent of each other, therefore we can write:

$P_n(t + dt) = P_n(t)$ . prob. no request in dt prob. no service completions in  $dt + P_n(t)$ . prob. one request in dt . prob. one service in  $dt + P_{n+1}(t)$ . prob. one service completed in dt . prob. no request in  $dt + P_{n-1}(t)$ . prob. one request in dt . prob. no service completion in dt + o(dt)

for

$$n \ge 1$$

(3)

The transition probabilities from state (m) to (m+1) will be:

prob. no request in dt = [1-(N-m) Rdt - o(dt)]

prob. no service completions in dt = [1 - Sdt - o(dt)]

prob. one request in dt = (N-m) R dt + o(dt)

prob. one service in dt =

$$Sdt + o(dt)$$

for m=n-1, n, n+1 (4)

We substitute the above transition probabilities to the differential equation (3) and combining all O(dt) terms and realising terms with (dt)<sup>2</sup> are also O(dt), we get,:

$$\begin{split} P_{n}(t+dt) &= P_{n}(t) \left[ 1 - (N-n) \, Rdt - Sdt \right] \, + \\ &\quad P_{n+1}(t) \, \left[ Sdt \right) + P_{n-1}(t) & (5) \\ &\quad \left[ N - (n-1) \right) \, Rdt \right] \quad \text{for o> n> N.} \end{split}$$

While, for the limiting states, n=0 and n=N

$$\begin{split} P_{o}(t+dt) &= P_{o}(t) \; [1-N\,Rdt] \; + P_{1}(t) \; [Sdt] \\ n &= o \\ P_{N}(t+dt) &= P_{N}(t) \; [1-Sdt] \; + P_{n-1}(t) \; [Rdt] \\ n &= N \\ (6) \end{split}$$

We can rewrite the three above equations (5, 6) slightly differently to yield differential-difference equations;

$$\frac{P_n(t+dt) - P_n(dt)}{dt} = \frac{d}{dt} P_n(t)$$

$$\frac{d}{dt} P_{o}(t) = -N R P_{o}(t) + S P_{1}(t) \qquad (n=o)$$

$$\frac{d}{dt} P_{n}(t) = -[(N-n) R + S] P_{n}(t) + (n-n+1) R P_{n-1}(t) + S P_{n+1}(t)$$

$$(o>n>N)$$

$$\frac{d}{dt} P_{n}(t) = -S P_{n}(t) + R P_{n-1}(t)$$

$$(n=N)$$

(7)

To get the steady-state solution for  $P_n$ , the probability of n units waiting in the system at an arbitrary point of time after steady state is reached, we take the limit as  $t\to\infty$  of equations (7), when  $P_n(t)$  is independent of time,  $d P_n(t)/dt$  is zero, and we have:

$$-N R P_{o} + S P_{1} = 0 (n=0)$$

$$-[(N-n) R + S] P_{n} + (N-n+1) R P_{n-1} + (n-n+1$$

From these equations (8) we can find the recursion formula

$$P_{1} = N (R/S) P_{0}$$

$$P_{2} = (N-1) (R/S) P_{1}$$

$$P_{3} = (N-2) (R/S) P_{2}$$

$$P_{n+1} = (N-n) (R/S) P_{n}$$

(9)

Now we have to solve a set of difference equations, to find the probability distribution of the random variable (n)

$$P_{n} = \frac{N!}{(R/S)^{n}} \cdot P_{0}$$

(10)

Since the boundary condition

$$\sum_{n=0}^{N} P_n = 1 \tag{11}$$

We can evaluate Po as:

$$P_{O} = \frac{1}{\sum_{n=0}^{N} (R/S)^{n} \cdot \frac{N!}{(N-n)!}}$$

(12)

The steady state probability distribution for the subsystem and whole multi-processors organization will be computed and will be graphically represented for various N and (R/S). (see Fig. 5 in the results of simulation). The expected number of processors or I/O units in the system is:

$$L = \sum_{n=0}^{N} nP_n = N - \frac{S}{R} (1 - P_0)$$

and the mean number of waiting units in the queue will be

$$L_q = \sum_{n=1}^{N} (n-1) P_n = \sum_{n=1}^{N} n P_n - (1-P_0)$$

$$L_q = N - \frac{R+S}{R} (1 - P_o)$$

Now, we can proceed to derive the average waiting time in the queue W<sub>q</sub> and system (W) in the base of the FIFS (first in, first served) queue discipline.

$$W_q = \frac{L_q}{\Gamma(27.7)}$$

$$W = W_q + \frac{1}{S} = W_q + T_s$$

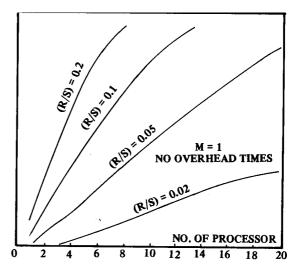

The other important parameter in such multiprocessors organization is a stretching factor, which is the ratio of the time needed to execute a program with conflict to access to memory (TC), to the necessary time to execute that piece of program without the presence of contention (Ts) i.e.,

S. F. =

$$\frac{T_c}{T_s}$$

$$T_c = W_q + T_s$$

S. F. =  $\frac{W_q + T_s}{T_s} = 1 + \frac{W_q}{T_s}$  (16)

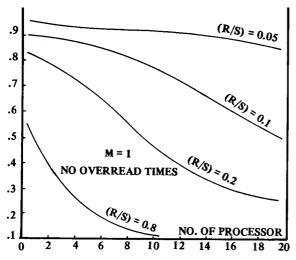

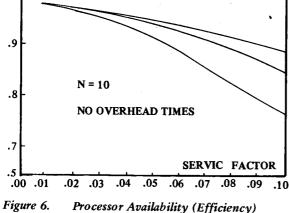

To derive the unit availability or processor and memory efficiency in the multi-processors organisation which all units are shared memory units, let N represent the number of units and represent the number of those units waiting in the system. We can also define the processor and memory efficiency as the proportion of the processor's or memory's time for which they are engaged in useful tasks. So we have:

P. E. =

$$\frac{N-L}{N}$$

(17)

memory efficiency =  $1 - P_0$

Results of Waiting Line Model Simulation: The following discussion is essential for an understanding of how the waiting line model works.

Our objective is to develop a model that is flexible to study several possible system configurations. Using this model, it should be possible to analyse different systems, of different sizes, using the same formulas already derived. The simulation program written to implement the model are general so that a system of any size can be studied over any range of the parameter involved. However, the results reported here are limited to systems with not more than 20 unit requestors and 20 memory units for different values of (R/S).

In a subsystem of multi-processors the

main memory is shared by all the processors and I/O, S, is also used as the "mail box" to pass messages between the processors. In addition to the shared memory, each processor has a "private" or "Local memory"; each of which can be accessed by only one processor. Local memories are used to store codes, tables of frequently used subroutines, tables for allocation of some private resources, etc, since the local memories do not communicate with each other. In a multi-microprocessor organization each processor can independently execute its own instructions. The interval of time until it becomes necessary to access a system data base is described by a negative exponential distribution function with parameter R and could be expressed by:

$$A(t) = 1 - e^{-Rt}$$

(continuous dist.)

$$P_n(t) = \frac{(Rt)^n}{n} e^{-Rt}$$

(discrete dist.)

R

$$n = 0, 1, \dots (18)$$

The expected execution interval for such a processor has a value  $T_s = \frac{1}{R}$  unit times.

The effect of I/O activity will not be modelled explicity. However, corresponding to tI/O and the overlapping, a fraction r<sub>1</sub> of the memory system time can be apportioned to I/O, S. The following figures show some representation of samples of several parameters. These parameters are:

The number or waiting units in the queue, the mean idle time for memory processors availability, memory efficiency, and finally the stretching factor in the system for several values of R/S.

Figure 5 shows a graphical representation

```

TYPE IN TWO PERCENTAGE NUMBER FOR YOUR ORGANISATION FESTING TIME O DECISION MAKING TIME - O

OF WAITING UNITS IN THE SYSTEM - .55-01

OF WAITING UNITS IN THE SYSTEM - .75923

OF WAITING UNITS IN THE GUEUE - .75923

E SIRECTULING PACTOR IN THE SYSTEM - .6433

FORTUNITY EFFICIENCY (AVAILIBILITY) - .462037

1376785-02 11s

1326876-02 11s

1326876-03 11s

1326876-03 11s

1326876-03 11s

1326876-03 11s

1326876-03 11s

1326876-03 11s

7578524-73 Th

200846-02 Hz

200846-02 Hz

200846-02 Hz

200846-02 Hz

2177486-01 Hz

221799 Hz

221799 Hz

221799 Hz

221799 Hz

221799 Hz

2374436-01 Hz

25744366-01 Hz

OF MAITING UNITS IN THE SYSTEM

OF MAITING UNITS IN THE SYSTEM

OF MAITING UNITS IN THE OUGLE

RAGE NUMBER OF IDLE MEMORY UNITS

STRETCHING FACTOR IN THE OUGLE

RATING UNIT EFFICIENCY

ORY UNIT EFFICIENCY AVAILEBILITY)

ORY UNIT EFFICIENCY AVAILEBILITY)

17/4598C-04 118

17/4598C-04 118

17/1688C-04 118

17/1688C-05 118

(1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5) - (1/5)

.759243 I 8

2.14582 I

5.09192 I

6.02123 I

6.67222 1

7.1445 I

7 - 50054

7.77797 I

B.0000B I

8.18185

8.33335

8.46155

8.57143

8.66667 1

0.82353 1

```

The Results of Waiting Line Model Figure 5. Simulation

of the distribution of Pn(probabilities of n units waiting in the system) for various values of (R/S) in order of n=0, 1, 2, ..., N.

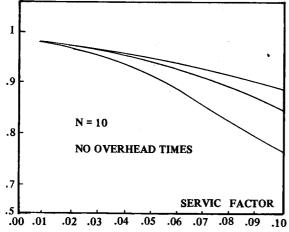

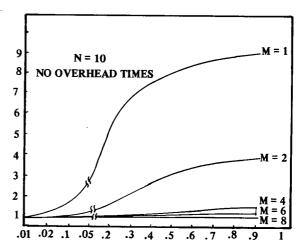

Figure 6 and 7 show processor and memory availability versus (N) for several values of (R/S). Figure 8 shows the stretching factor plotted against N for several different values of R/S. However, in general performance of the system can be improved (increased) by adding more memory units to a system with fixed R/S.

Figure 7. Memory Availability (Efficiency)

Stretching Factor in the System for Various Memory Units

### **CONCLUSIONS**

This paper is concerned with the theoretical evaluation of the performance of multiprocessors organisation, multi-microcomputers network.

A series of markovian waiting line models have been developed for multi-systems configurations with shared menories. The model is used to obtain quantitative results for system performance in terms of various parameters, such as:

Waiting and idle times, processor and

memory efficiency, stretching factor for program execution, and rate of instruction execution.

The objectives of this investigation are: 1— The ability to model existing and proposed multi-systems organisation.

- 2— To provide a facility to compare different multi-systems organisations, through system performance.

- 3- To enable one to measure the performance of available multi-processors-organisations.

- 4— To enable one to create and tailored a new multi-computers organisation to a particular application.

From the point of view of practical design in a multiprocessors and multi-microsnetwork organisations, the main memories are shared by all units such as processors and input-loutput units. A single copy of the operating system in this shared memory controls the entire system, since this shared memory should be accessible by all the units.

In addition to the shared memories each processor unit can have a private or local read/write memory and read only memory (ROM).

Three classes of system have been distinguished:

- 1- System without local and Rom memories.

- 2- System with local memory.

- 3— System with local memory and ROM. (Computer).

During system activity each memory unit is required to attend to a number of processors and I/O's which request access to that memory. The memory conflict occurs whenever two or more units attempt to access the same memory unit simultaneously. The overal offect of these conflicts is referred to as

memory interfevence. The result is a loss of the system efficiency which is said to arise due to interference. Obviously, if the number of processors assigned to the one memory unit becomes large, the loss of efficiency due to interference increases. On the other hand. if fewer processors are assigned to the memory, the price per performance increases. Hence, the problem is to determine the number of processors to be assigned to a memory unit so as to minimise output costs by balancing the cost of the memory units in the system against the loss of efficiency due to units interference. It is clear that the lower values of servicing factors (RIS) create the greater idle time for memory units, fewer waiting units, smaller stretching factors and faster response time for a system. However, this may be an uneconomical design.

The economical constraints require that a good choice of relative memory and processor speed and efficiencies be made by choosing a certain value of R/S or N x  $\frac{R}{S}$  during the design of a multi-processors organisation.

#### REFERENCES

- Karuh, J.: "On the Chapman-Kolmogorov equation", Ann. Math. statist, Vol 32, 1961, pp. 1333-1337.

- Lorin, H.: "Parallelism in hardware and software; Real and apparent concurrency" Prentice-Hall Inc, 1972.

- Anacker, W. & Wang C. P: "Performance evaluation of Computing systems with memory hierachies", IEEE Trans. On comp. EC-16 1967, 764-772.

- Enslow, P. H. Jr.: "Multiprocessors and parallel processing", John wiley & Sons, New York, 1974.

- Computing Surveys: Special Issue; "Parallel Processors and Processing", Vol. 9, No. 1, March 1977.

- Skinner, C. E. & Asher, J. R.: "Effects of storage contention on system performance" IBM syst. J., Vol 8, No 4, 1969, 319-333.

- Burnett, G. J.: "Performance analysis of interleaved memory system", Ph. D Thesis, Princeton university, 1969.